Dan NICULA

ELECTRONIC

˘

A DIGITAL

˘

A

Carte de ˆınv˘at¸˘atur˘a 2.0

Editura Universit˘at¸ii TRANSILVANIA din Bra¸sov

ISBN 978-606-19-0563-8

2015

Lect¸ia 3

Port¸i logice

3.1 Not¸iuni teoretice

O poart˘a logic˘a este un circuit electronic care implementeaz˘a o funct¸ie logic˘a. Port¸ile logice au asociate simboluri

grafice.

NOT AND NAND OR NOR XOR XNOR

A B A A · B A · B A + B A + B A ⊕ B A ⊕ B

0 0 1 0 1 0 1 0 1

0 1 1 0 1 1 0 1 0

1 0 0 0 1 1 0 1 0

1 1 0 1 0 1 0 0 1

Not¸iunea de poart˘a se justific˘a prin faptul c˘a se poate considera c˘a unul din semnale condit¸ioneaz˘a trecerea altui

semnal prin circuit.

Logica Boolean˘a opereaz˘a cu dou˘a valori: adev˘arat ¸si fals. Acestor valori li se pot asocia pe mult¸imea binar˘a dou˘a

valori numerice: 0 = fals, 1 = adev˘arat.

Evaluarea valorii de adev˘ar a unei expresii formate din propozit¸ii simple este posibil˘a prin considerarea unor operatori

de negare, conjunct¸ie ¸si disjunct¸ie.

Tabelele de adev˘ar al operatorilor sunt:

NOT AND OR

A A A B A · B A B A + B

0 1 0 0 0 0 0 0

1 0 0 1 0 0 1 1

1 0 0 1 0 1

1 1 1 1 1 1

Pe baza celor 3 operatori, se pot defini operatori compu¸si, conform tabelelor de adev˘ar:

NAND NOR XOR XNOR

A B A · B A B A + B A B A ⊕ B A B A ⊕ B

0 0 1 0 0 1 0 0 0 0 0 1

0 1 1 0 1 0 0 1 1 0 1 0

1 0 1 1 0 0 1 0 1 1 0 0

1 1 0 1 1 0 1 1 0 1 1 1

34 LECT¸ IA 3. Port¸i logice

3.2 Pentru cei ce vor doar s˘a promoveze examenul

1. S˘a se determine port¸ile logice echivalente port¸ilor:

a) A · B b) A + B c) A · B · C d) A + B + C

Solut¸ie

O poart˘a logic˘a echivalent˘a se obt¸ine prin negarea atˆat a intr˘arilor cˆat ¸si a ie¸sirilor ¸si interschimbarea operatorilor

logici AND ⇔ OR. Transformarea se poate justifica analitic aplicarea teoremei lui DeMorgan. Eventual, anterior

aplic˘arii teoremei lui DeMorgan se aplic˘a ˆıntregii expresii o dubl˘a negare.

a) A · B = A · B = A + B = A + B

c) A · B · C = A + B + C == A + B + C

2. S˘a se determine structura de port¸i logice care realizeaz˘a urm˘atoarea funct¸ie logic˘a:

Y = (A · B + C + D) · E · F · G

Solut¸ie

Structura de port¸i reprezint˘a o implementare a operatorilor prezent¸iˆın expresia funct¸iei, t¸inˆand cont de precedent¸a

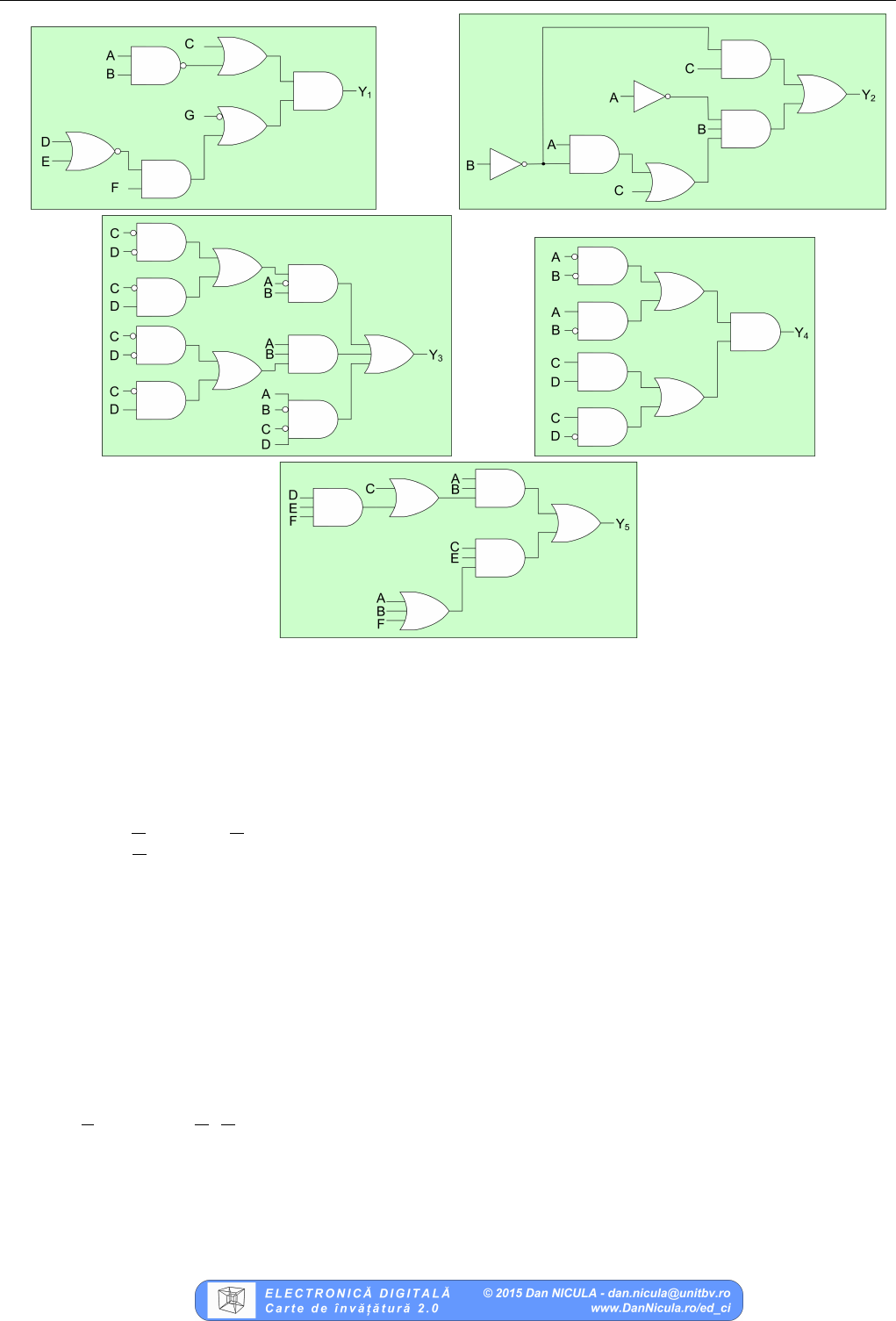

acestora (figura 3.1).

Figura 3.1 Structura de port¸i logice pentru implementarea funct¸iei de la problema 2.

3. S˘a se determine funct¸ia logic˘a a structurii de port¸i logice prezentate ˆın figura 3.2.

Figura 3.2 Structura de port¸i logice (problema 3).

4. Desenat¸i diagramele temporale asociate circuitelor cu port¸i logice prezentate ˆın figura 3.3.

Solut¸ie

Circuitul are trei intr˘ari: A, B ¸si C. Stimulii de intrare vor avea 2

3

= 8 valori diferite. Pentru fiecare combinat¸ie

de intrare se determin˘a valoarea logic˘a a ie¸sirii port¸ilor, ˆın funct¸ie de tipul acesteia.

D = A + B, E = D · C

Formele de und˘a pentru D ¸si E se determin˘a prin aplicarea funct¸iilor ment¸ionate pentru toate combinat¸iile

intr˘arilor. O alternativ˘a const˘a ˆın utilizarea unui tabel de adev˘ar pentru centralizarea datelor.

3.3. Pentru cei ce vor s˘a ˆınvet¸e 35

Figura 3.3 Circuite cu port¸i logice ¸si diagrame temporale asociate (problema 4).

A B C B C D = A + B E = D · C

0 0 0 1 1 1 1

0 0 1 1 0 1 0

0 1 0 0 1 0 0

0 1 1 0 0 0 0

1 0 0 1 1 1 1

1 0 1 1 0 1 0

1 1 0 0 1 1 1

1 1 1 0 0 1 0

3.3 Pentru cei ce vor s˘a ˆınvet¸e

1. S˘a se demonstreze c˘a urm˘atoarele seturi de operatori logici sunt complete. Prezentat¸i modul de realizare a

tuturor operatorilor logici (NOT, AND, NAND, OR, NOR, XOR, XNOR) utilizˆand numai port¸ile din setul

complet.

• {AND, NOT}

• {NAND}

• {OR, NOT}

• {NOR}

• {XOR, AND}

Solut¸ie

ˆ

In figura 3.4 este prezentat modul de realizare a operatorilor logici NOT, AND, NAND, OR, NOR, XOR ¸si

XNOR utilizˆand doar port¸ile din seturile complete {AND, NOT}, {NAND}, {OR, NOT}, {NOR} ¸si {XOR,

AND}.

2. Justificat¸i semnificat¸ia de ”poart˘a logic˘a” p entru port¸ile logice: AND, OR, XOR, NOR, NAND.

Solut¸ie

Se consider˘a port¸ile cu dou˘a intr˘ari. Dac˘a se denume¸ste o intrare data ¸si o intrare validare, se pot g˘asi

urm˘atoarele semnificat¸ii ale funct¸ion˘arii port¸ilor logice.

AND: Dac˘a validare = 1, trece data (poarta este deschis˘a).

Dac˘a validare = 0, la ie¸sire este ˆıntotdeauna 0 (poarta este blocat˘a pentru data).

OR: Dac˘a validare = 0, trece data (poarta este deschis˘a).

Dac˘a validare = 1, la ie¸sire este ˆıntotdeauna 1 (poarta este blocat˘a pentru data).

XOR: Dac˘a validare = 0, trece data (poarta este deschis˘a).

Dac˘a validare = 1, trece data (poarta este deschis˘a ca un inversor).

NAND: Dac˘a validare = 1, trece data (poarta este deschis˘a ca un inversor).

36 LECT¸ IA 3. Port¸i logice

NOT AND NAND OR

AND, NOT

NAND

OR, NOT

NOR

XOR, AND

NOR XOR XNOR

AND, NOT

NAND

OR, NOT

NOR

XOR, AND

Figura 3.4 Realizarea operatorilor logici cu operatori din seturi complete (problema 1).

Dac˘a validare = 0, la ie¸sire este ˆıntotdeauna 1 (poarta este blocat˘a pentru data).

NOR: Dac˘a validare = 0, trece data (poarta este deschis˘a ca un inversor).

Dac˘a validare = 1, la ie¸sire este ˆıntotdeauna 0 (poarta este blocat˘a pentru data).

3. S˘a se determine port¸ile logice echivalente port¸ilor:

a) A · B b) A · B · C c) A · B d) A + B + C

Solut¸ie

O poart˘a logic˘a echivalent˘a se obt¸ine prin negarea atˆat a intr˘arilor cˆat ¸si a ie¸sirilor ¸si interschimbarea operatorilor

logici AND ⇔ OR. Figura 3.5 prezint˘a port¸i logice echivalente.

4. S˘a se determine structura de port¸i logice care realizeaz˘a urm˘atoarea funct¸ie logic˘a:

Y = (A · B · C + D) · E · F + G · H · (I + J + K)

Solut¸ie

Structura de port¸i este prezentat˘a ˆın figura 3.6.

3.3. Pentru cei ce vor s˘a ˆınvet¸e 37

Figura 3.5 Port¸i logice echivalente (problema 3).

Figura 3.6 Structura de port¸i logice (problema 4).

5. S˘a se determine structurile de port¸i logice care realizeaz˘a urm˘atoarele funct¸ii logice. S˘a se simplifice expresiile

utilizˆand prelucr˘ari analitice ¸si s˘a se determine structurile de port¸i logice simplificate.

a) Y

1

= (A · B + C) · [(D + E) · F + G];

b) Y

2

= (A · B + C) · A · B + B · C;

c) Y

3

= A · B · (C · D + C · D) + A · B · (C · D + C · D) + A · B · C · D;

d) Y

4

= (A · B + A · B) · (C · D + C · D);

e) Y

5

= A · B · (C + D · E · F ) + C · E · (A + B + F ).

Solut¸ie

Structurile de port¸i sunt prezentate ˆın figura 3.7.

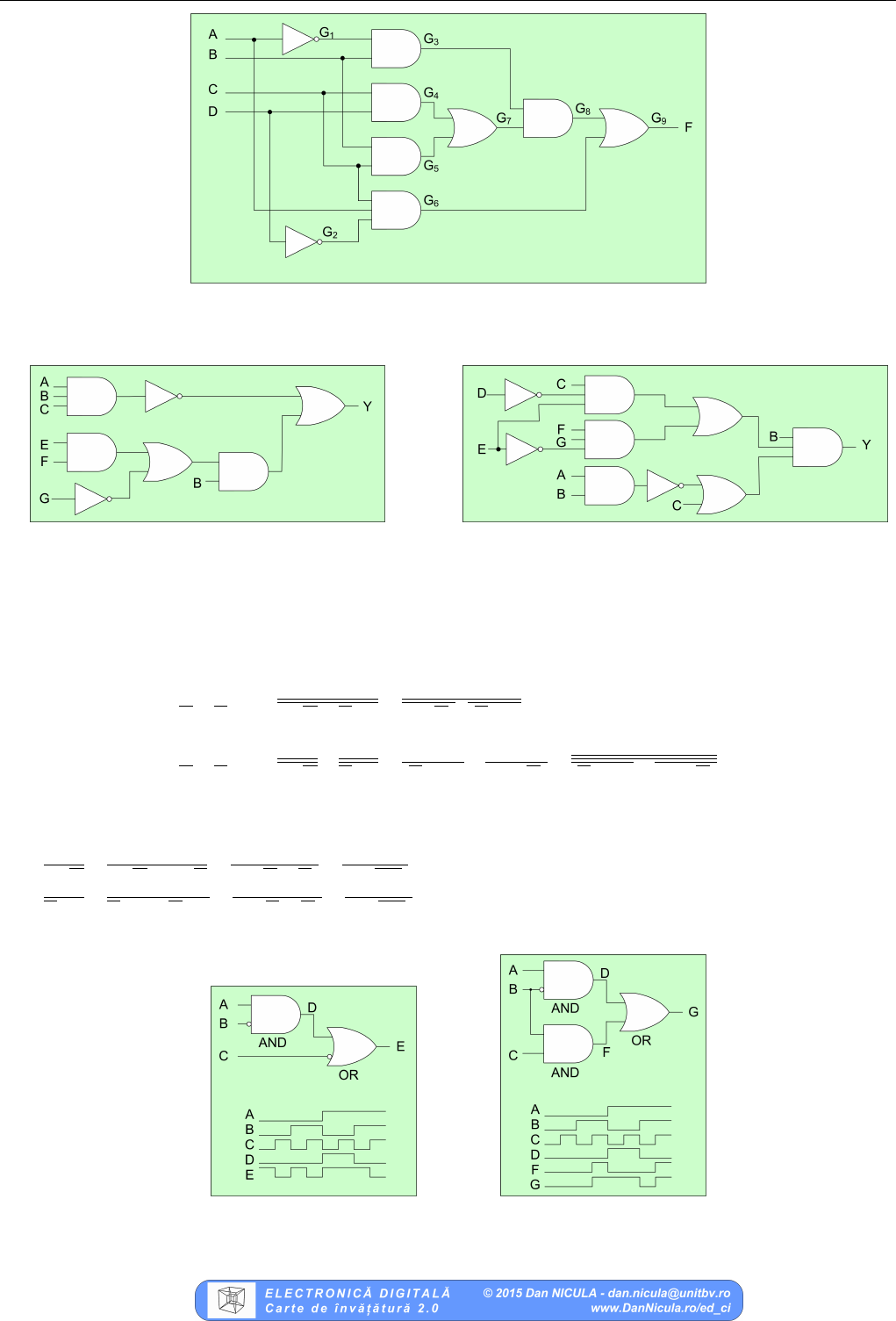

6. S˘a se determine funct¸ia logic˘a a structurii de port¸i logice prezentate ˆın figura 3.8.

Solut¸ie

Pornind de la intrarea ret¸elei spre ie¸sire, dup˘a fiecare poart˘a se determin˘a expresia logic˘a a ie¸sirii respective care

este apoi propagat˘a la intrarea urm˘atoarelor port¸i logice. Pentru ret¸eaua din figura 3.8, la ie¸sirile port¸ilor se

deduc:

G

1

= A

G

2

= D

G

3

= G1 · B = A · B

G

4

= C · D

G

5

= B · C

G

6

= A · C · G

2

= A · C · D

G

7

= G

4

+ G

5

= C · D + B · C

G

8

= G

3

· G

7

= (A · B) · (C · D + B · C)

G

9

= F = G

6

+ G

8

= A · C · D + A · B · (C · D + B · C) = A · C · D + A · B · C · D + A · B · C.

7. Determinat¸i funct¸iile logice implementate de structurile de port¸i logice din figura 3.9.

Solut¸ie

a) Y = A · B · C + (E · F + G) · B

b) Y = B · (C · D · E + F · G · E) · (A · B + C)

38 LECT¸ IA 3. Port¸i logice

a) b)

c) d)

e)

Figura 3.7 Structuri de port¸i logice (problema 5).

8. Desenat¸i diagramele temporale asociate circuitelor cu port¸i logice prezentate ˆın figura 3.10-a,b.

Solut¸ie

Circuitele au trei intr˘ari: A, B ¸si C. Stimulii de intrare vor avea 2

3

= 8 valori diferite. Pentru fiecare combinat¸ie

de intrare se determin˘a valoarea logic˘a a ie¸sirii port¸ilor, ˆın funct¸ie de tipul acesteia.

a) D = A · B, E = D + C

b) D = A · B, F = B · C, G = D + F

Diagramele temporale sunt prezentate ˆın aceea¸si figur˘a 3.10-a,b.

9. Determinat¸i tipul port¸ilor logice caracterizate de diagramele temporale prezentate ˆın figura 3.11. A, B ¸si C sunt

intr˘ari iar D ¸si E sunt ie¸siri.

Solut¸ie

Diagramele temporale prezint˘a formele de und˘a ale intr˘arilor A, B, C ¸si ale ie¸sirilor D ¸si E. Se observ˘a c˘a

diagramele prezint˘a toate combinat¸iile intr˘arilor, 2

3

= 8.

ˆ

In primul caz, se remarc˘a faptul c˘a ie¸sirea D este egal˘a cu 1 dac˘a un num˘ar impar de intr˘ari sunt egale cu 1.

Aceasta implic˘a relat¸ia:

D = A ⊕ B ⊕ C.

ˆ

In al doilea caz, funct¸ia este:

E = A · B · C + A · B · C + A · B · C.

Implementarea direct˘a a funct¸iei este prezentat˘a ˆın figura 3.12. Alternativa este s˘a se realizeze tabelul de adev˘ar

¸si s˘a se completeze coloanele ie¸sirilor pe baza formelor de und˘a. Ulterior, expresia funct¸iei se poate deduce din

tabelul de adev˘ar.

10. S˘a se implementeze funct¸ia logic˘a F = A ⊕ B cu port¸i:

a) NAND cu dou˘a intr˘ari;

3.3. Pentru cei ce vor s˘a ˆınvet¸e 39

Figura 3.8 Structura de port¸i logice (problema 6).

a) b)

Figura 3.9 Structura de port¸i logice (problema 7).

b) NOR cu dou˘a intr˘ari.

Solut¸ie

Pentru implementarea cu port¸i NAND, funct¸ia F se rescrie:

F = A ⊕ B = A · B + A · B = A · B + A · B = (A · B) · (A · B)

Pentru implementarea cu port¸i NOR, funct¸ia F se rescrie:

F = A ⊕ B = A · B + A · B = A · B + A · B = (A + B) + (A + B) = (A + B) + (A + B)

Ambele implement˘ari sunt reprezentate ˆın figura 3.13.

Se observ˘a c˘a ˆın ambele implement˘ari anterioare sunt necesare dou˘a port¸i pentru realizarea intr˘arilor negate. Se

pot rescrie expresiile pentru a se pune ˆın evident¸˘a termeni comuni astfel:

A · B = A · B + A · A = A · (B + A) = A · (AB)

A · B = A · B + B · B = B · (A + B) = B · (AB)

a) b)

Figura 3.10 Circuite cu port¸i logice ¸si diagrame temporale asociate (problema 8).

40 LECT¸ IA 3. Port¸i logice

Figura 3.11 Diagrame temporale (problema 9).

Figura 3.12 Circuite determinate pe baza diagramelor temporale prezentate ˆın figura 3.11 (problema 9).

Deci: F = A ⊕ B = A · (A · B).B · (A · B).

Similar:

A + B = (A + B) + B

A + B = A + (A + B)

Deci: F = A ⊕ B = (A + B) + B + A + (A + B).

Cele dou˘a implement˘ari optimizate sunt prezentate ˆın figura 3.14.

11. Justificat¸i afirmat¸ia c˘a poarta logic˘a XOR implementeaz˘a un circuit de adunare a doi bit¸i.

Solut¸ie

Tabelul de adev˘ar al funct¸iei logice XOR ¸si al adun˘arii p e 2 bit¸i este prezentat ˆın continuare.

A B A ⊕ B A + B (plus)

0 0 0 0

0 1 1 1

1 0 1 1

1 1 0 0

Se observ˘a egalitatea coloanelor aso ciate funct¸iei logice XOR ¸si a funct¸iei matematice de adunare.

12. Justificat¸i afirmat¸ia c˘a poart˘a logic˘a AND implementeaz˘a un circuit de ˆınmult¸ire a doi bit¸i.

Solut¸ie

Tabelul de adev˘ar al funct¸iei logice AND ¸si al ˆınmult¸irii pe 2 bit¸i este prezentat ˆın continuare.

Figura 3.13 Implementarea funct¸iei XOR cu port¸i NAND ¸si NOR (problema 10).

3.3. Pentru cei ce vor s˘a ˆınvet¸e 41

Figura 3.14 Implementarea funct¸iei XOR cu port¸i NAND ¸si NOR, optimizate (problema 10).

A B A · B A × B (ˆınmult¸ire)

0 0 0 0

0 1 0 0

1 0 0 0

1 1 1 1

Se observ˘a egalitatea coloanelor aso ciate funct¸iei logice AND ¸si a funct¸iei matematice de ˆınmult¸ire.

13. Operat¸iile logice cu ¸siruri de bit¸i (bus-uri de date) se efectueaz˘a considerˆand fiecare bit separat (operat¸ii ”bit cu

bit”). Se consider˘a urm˘atoarele bus-uri de 8 bit¸i: A = 10101101 ¸si B = 10001110.

Determinat¸i rezultatul operat¸iilor: A · B, A · B, A + B, A + B, A ⊕ B, A ⊕ B, A, B.

Solut¸ie

A · B = 1010 1101 · 1000 1110 = 1000 1100;

A · B = 1010 1101 · 1000 1110 = 0111 0011;

A + B = 1010 1101 + 1000 1110 = 1010 1111;

A + B = 1010 1101 + 1000 1110 = 01010 000;

A ⊕ B = 1010 1101 ⊕ 1000 1110 = 0010 0011

A ⊕ B = 1010 1101 ⊕ 1000 1110 = 1101 1100

A = 1010 1101 = 0101 0010

B = 1000 1110 = 0111 0001.

14. Implementat¸i funct¸iile F = X · Y + X · Y + Y · Z ¸si G = A · B · C + A · C + A · B cu:

a) port¸i AND, OR ¸si NOT,

b) port¸i OR ¸si NOT,

c) port¸i AND ¸si NOT.

Solut¸ie

Implementarea cu port¸i (AND, OR, NOT) se face direct din expresia prezentat˘a (sum˘a de produse).

Implementarea cu port¸i (AND, NOT) se face prin modificarea operatorului OR cu o structur˘a de port¸i echivalente

folosind port¸i AND ¸si NOT (a¸sa cum este prezentat ˆın figura 3.4).

Analitic, transformarea funct¸iei se face prin aplicarea dublei negat¸ii ¸si a teoremei lui DeMorgan asupra sumei.

F = X · Y + X · Y + Y · Z = X · Y + X · Y + Y · Z = X · Y · X · Y · Y · Z

Implementarea cu port¸i (OR, NOT) se face prin modificarea operatorului AND cu o structur˘a de port¸i echivalente

folosind port¸i OR ¸si NOT (a¸sa cum este prezentat ˆın figura 3.4).

Analitic, transformarea funct¸iei se face prin aplicarea dublei negat¸ii ¸si a teoremei lui DeMorgan asupra produselor.

F = X · Y + X · Y + Y · Z = X · Y + X · Y + Y · Z = X + Y + X + Y + Y + Z

Structurile sunt prezentate ˆın figura 3.15.

15. Precizat¸i port¸i logice echivalente (opt¸ional cu intr˘ari sau ie¸siri negate) pentru circuitele prezentate ˆın figura 3.16.

16. Precizat¸i circuitele logice echivalente cu port¸i NAND pentru circuitele prezentate ˆın figura 3.17.

17. Determinat¸i structura de port¸i logice care implementeaz˘a funct¸iile, f˘ar˘a a le simplifica. Simplificat¸i funct¸iile prin

prelucr˘ari algebrice ¸si propunet¸i o structur˘a de port¸i logice simplificat˘a.

42 LECT¸ IA 3. Port¸i logice

AND, OR, NOT AND, NOT OR, NOT

F = X · Y + X · Y + Y · Z

F = X · Y + X · Y + Y · Z F = X · Y · X · Y · Y · Z F = X + Y + X + Y + Y + Z

G = A · B · C + A · C + A · B

G = A · B · C + A · C + A · B G = A · B · C · A · C · A · B G = A + B + C + A + C + A + B

Figura 3.15 Realizarea operatorilor logici cu operatori din seturi complete (problema 14).

Figura 3.16 Circuite logice (problema 15).

a) B · C + A · B + A · C · D d) (A · B + A · B) · (C · D + C · D)

b) (A + B) · (C + D) · (A + B + D) e) W · X · Y + W · Z + X · Y

c) A · (B · C + B · C) + C · (B · D + B · D) f) W · Y · (X + Z) + X · Y · (W + Z) + W · Z · (X + Y )

18. Se consider˘a funct¸ia logic˘a F = X · Y · Z + X · Y · Z + W · X · Y + W · X · Y + W · X · Y

a) Obt¸inet¸i tabelul de adev˘ar al funct¸iei.

b) Determinat¸i structura de port¸i logice care implementeaz˘a funct¸ia, conform expresiei originale.

c) Simplificat¸i expresia funct¸iei utilizˆand alegebra Boolean˘a.

d) Obt¸inet¸i tab elul de adev˘ar al funct¸iei din expresia simplificat˘a ¸si demonstrat¸i c˘a este identic cu cel obt¸inut

anterior.

e) Determinat¸i structura de port¸i logice care implementeaz˘a funct¸ia, conform expresiei minimizate.

f) Comparat¸i costurile celor dou˘a implement˘ari ca num˘ar de port¸i logice ¸si ca num˘ar de intr˘ari ˆın port¸i logice.

Solut¸ie

a) Tabelul de adev˘ar al funct¸iei ¸si structura de port¸i sunt prezentate ˆın figura 3.18.

c) F = X · Y · Z + X · Y · Z + W · X · Y + W · X · Y + W · X · Y = Y · Z · (X + X) + X · Y · (W + W ) + W · X · Y =

Y · Z + X · Y + W · X · Y = Y · Z + Y · (X + X · W ) = Y · Z + Y · (X + W ) = Y · Z + Y · X + Y · W

Figura 3.17 Circuite logice (problema 16).

3.3. Pentru cei ce vor s˘a ˆınvet¸e 43

Init¸ial W X Y Z F Simplificat

0 0 0 0 0

0 0 0 1 1

0 0 1 0 0

0 0 1 1 0

0 1 0 0 0

0 1 0 1 1

0 1 1 0 1

0 1 1 1 1

1 0 0 0 0

1 0 0 1 1

1 0 1 0 1

1 0 1 1 1

1 1 0 0 0

1 1 0 1 1

1 1 1 0 1

1 1 1 1 1

Figura 3.18 Tabelul de adev˘ar ¸si structura de port¸i logice init¸ial˘a ¸si simplificat˘a (problema 18).

f) Costurile implement˘arii, calculate ca num˘ar de port¸i logice ¸si ca num˘ar de intr˘ari ˆın port¸i logice, sunt:

Implementare init¸ial˘a: Implementare dup˘a simplificare:

3 port¸i NOT × 1 intrare; 1 poart˘a NOT × 1 intrare;

5 port¸i AND × 3 intr˘ari; 3 port¸i AND × 2 intr˘ari;

1 poart˘a OR × 5 intr˘ari. 1 poart˘a OR × 3 intr˘ari.

Total: 9 port¸i × 23 intr˘ari. Total: 5 port¸i × 10 intr˘ari.

19. Un circuit logic are trei intr˘ari ¸si dou˘a ie¸siri. O ie¸sire este egal˘a cu 1 dac˘a toate intr˘arile sunt egale cu 1. A doua

ie¸sire este egal˘a cu 0 dac˘a dou˘a sau mai put¸in de dou˘a intr˘ari sunt egale cu 0. S˘a se determine tabelul de adev˘ar

al funct¸iilor ¸si expresiile analitice ale acestora.

Solut¸ie

Definirea celei de-a doua funct¸ii este similar˘a cu: ”ie¸sirea este egal˘a cu 0 dac˘a exist˘a 0, 1 sau 2 intr˘ari egale

cu 0”, adic˘a ”ie¸sirea este egal˘a cu 1 dac˘a exist˘a 3 intr˘ari egale cu 0”. Tabelul de adev˘ar al celor dou˘a funct¸ii este:

A B C O

1

O

2

0 0 0 0 1

0 0 1 0 0

0 1 0 0 0

0 1 1 0 0

1 0 0 0 0

1 0 1 0 0

1 1 0 0 0

1 1 1 1 0

Expresiile analitice ale ie¸sirilor sunt:

O

1

= A · B · C

O

2

= A · B · C = A + B + C

20. Determinat¸i funct¸ia logic˘a cu trei intr˘ari care este egal˘a cu 1 doar ˆın cazul ˆın care valoarea de la intrare (exprimat˘a

ˆın binar) este mai mic˘a decˆat 3. S˘a se determine tabelul de adev˘ar ¸si expresia ie¸sirii.

Solut¸ie

44 LECT¸ IA 3. Port¸i logice

Valoare A B C O

0 0 0 0 1

1 0 0 1 1

2 0 1 0 1

3 0 1 1 0

4 1 0 0 0

5 1 0 1 0

6 1 1 0 0

7 1 1 1 0

Expresia ie¸sirii este: O = A · (B + C).

21. Proiectat¸i un circuit logic cu trei intr˘ari ¸si trei ie¸siri. Dac˘a valoarea de la intrare (exprimat˘a ˆın binar) este 0, 1,

2 sau 3 atunci ie¸sirea este mai mare cu o unitate fat¸˘a de intrare. Dac˘a valoarea de la intrare este 4, 5, 6, sau

7 atunci ie¸sirea este mai mic˘a cu o unitate fat¸˘a de intrare. S˘a se determine tabelul de adev˘ar ¸si expresiile celor

trei ie¸siri.

Solut¸ie

Valoare intrare I

2

I

1

I

0

O

2

O

1

O

0

Valoare ie¸sire

0 0 0 0 0 0 1 1

1 0 0 1 0 1 0 2

2 0 1 0 0 1 1 3

3 0 1 1 1 0 0 4

4 1 0 0 0 1 1 3

5 1 0 1 1 0 0 4

6 1 1 0 1 0 1 5

7 1 1 1 1 1 0 6

Expresiile analitice ale ie¸sirilor sunt:

O

2

= I

2

·I

1

·I

0

+I

2

·I

1

·I

0

+I

2

·I

1

·I

0

+I

2

·I

1

·I

0

= I

2

·I

1

·I

0

+I

2

·(I

1

·I

0

+I

1

·I

0

+I

1

·I

0

) = I

2

·I

1

·I

0

+I

2

·(I

1

·I

0

+I

1

·(I

0

+I

0

)) =

= I

2

· I

1

· I

0

+ I

2

· (I

1

· I

0

+ I

1

· 1) = I

2

· I

1

· I

0

+ I

2

· (I

1

· I

0

+ I

1

) = I

2

· I

1

· I

0

+ I

2

· (I

0

+ I

1

)

O

1

= I

2

⊕ I

1

⊕ I

0

, (se observ˘a c˘a O

1

= 1 dac˘a un num˘ar impar de intr˘ari sunt egale cu 1).

O

0

= I

0

, (se observ˘a coloana O

0

complementar˘a coloanei I

0

).

22. S˘a se proiecteze un circuit logic care s˘a compare 2 bit¸i A ¸si B producˆand 3 ie¸siri: E = 1 dac˘a A = B, L = 1

dac˘a A < B ¸si G = 1 dac˘a A > B.

Solut¸ie

Tabelul de adev˘ar al circuitului comparator este:

A B G E L

0 0 0 1 0

0 1 0 0 1

1 0 1 0 0

1 1 0 1 0

Din tabelul de adev˘ar, rezult˘a ecuat¸iile circuitului comparator de 1 bit ¸si structura de port¸i logice reprezentat˘a

ˆın figura 3.19:

G = A · B

E = A ⊕ B

L = A · B

3.4. Pentru cei ce vor s˘a devin˘a profesioni¸sti 45

Figura 3.19 Circuitul comparator de 1 bit: simbol bloc ¸si structur˘a de port¸i logice.

3.4 Pentru cei ce vor s˘a devin˘a profesioni¸sti

1. S˘a se proiecteze un circuit logic care s˘a compare 2 bit¸i A ¸si B ¸si care s˘a t¸in˘a cont de rezultatul comparat¸iei unor

bit¸i de pondere superioar˘a.

Solut¸ie

ˆ

In cazul propag˘arii rezultatelor compar˘arii de la bit¸ii mai semnificativi, circuitul are 5 intr˘ari (intr˘arile comparate

A ¸si B ¸si intr˘arile cu rezultatele compar˘arii bit¸ilor superiori G

i

, E

i

, L

i

) ¸si 3 ie¸siri (rezultatele compar˘arii bit¸ilor

curent¸i sau propagarea rezultatelor compar˘arii bit¸ilor superiori G

o

, E

o

, L

o

).

Tabelul de funct¸ionare al acestui circuit este:

G

i

E

i

L

i

A B G

o

E

o

L

o

Observat¸ii

0 0 0 X X X X X caz imposibil la intrare

0 0 1 X X 0 0 1 deja s-a determinat c˘a A < B

0 1 0 0 0 0 1 0

0 1 0 0 1 0 0 1 prin compararea bit¸ilor superiori,

0 1 0 1 0 1 0 0 s-a determinat pˆan˘a acum c˘a A = B

0 1 0 1 1 0 1 0

0 1 1 X X X X X caz imposibil la intrare

1 0 0 X X 1 0 0 deja s-a determinat c˘a A > B

1 0 1 X X X X X caz imposibil la intrare

1 1 0 X X X X X caz imposibil la intrare

1 1 1 X X X X X caz imposibil la intrare

Din tabelul de adev˘ar se deduc ecuat¸iile:

G

o

= G

i

+ E

i

· A · B A > B dac˘a din compararea bit¸ilor mai semnificativi s-a dedus c˘a

A > B (G

i

= 1) sau dac˘a pˆan˘a la acest index a fost egalitate (E

i

= 1) ¸si A

i

> B

i

.

E

o

= E

i

· A ⊕ B A = B dac˘a din compararea bit¸ilor mai semnificativi s-a dedus

egalitatea (E

i

= 1) ¸si bit¸ii curent¸i sunt deasemenea egali A

i

= B

i

.

L

o

= L

i

+ E

i

· A · B A < B dac˘a din compararea bit¸ilor mai semnificativi s-a dedus c˘a

A < B (L

i

= 1) sau dac˘a pˆan˘a la acest index a fost egalitate (E

i

= 1) ¸si A

i

< B

i

.

Ecuat¸iile de mai sus se pot deduce prin observarea cazului cˆand o anumit˘a ie¸sire este activat˘a, la parcurgerea

bit¸ilor de la cel mai semnificativ (stˆanga) spre cel mai put¸in semnificativ (dreapta). Comparatorul de index i va

realiza urm˘atoarele funct¸ii:

- Num˘arul A este mai mare decˆat B (G

o

= 1) dac˘a ˆın urma compar˘arii bit¸ilor superiori s-a decis c˘a A > B

(G

i

= 1) sau dac˘a ˆın urma compar˘arii bit¸ilor superiori s-a decis c˘a A = B (E

i

= 1) ¸si A

i

> B

i

.

- Num˘arul A este egal cu B (E

o

= 1) dac˘a ˆın urma compar˘arii bit¸ilor superiori s-a decis c˘a A = B (E

i

= 1) ¸si

prin compararea bit¸ilor curent¸i se constat˘a c˘a A

i

= B

i

.

- Num˘arul A este mai mic decˆat B (L

o

= 1) dac˘a ˆın urma compar˘arii bit¸ilor superiori s-a decis c˘a A < B

(L

i

= 1) sau dac˘a ˆın urma compar˘arii bit¸ilor superiori s-a decis c˘a A = B (E

i

= 1) ¸si A

i

< B

i

.

Figura 3.20 prezint˘a simbolul bloc ¸si structura de port¸i logice a circuitului comparator cu propagarea rezultatelor

compar˘arii de la bit¸ii superiori.

46 LECT¸ IA 3. Port¸i logice

Figura 3.20 Circuitul comparator de 1 bit cu propagarea rezultatelor compar˘arii bit¸ilor superiori: simbol bloc ¸si structur˘a de

p ort¸i logice.

2. Utilizˆand 4 instant¸ieri ale circuitului descris la problema 1, s˘a se proiecteze un circuit comparator a dou˘a cuvinte

de cˆate 4 bit¸i.

Solut¸ie

Compararea a dou˘a cuvinte de mai mult¸i bit¸i se poate face prin instant¸ierea mui multor celule de comparare

pe bit, conectate astfel ˆıncˆat s˘a propage rezultatele comp˘ar˘arii bit¸ilor mai semnificativi spre bit¸ii mai put¸in

semnificativi. Esent¸a comp˘ar˘arii este c˘a dac˘a prin compararea unor bit¸i (cei mai semnificativi) se decide c˘a un

num˘ar este mai mare, nu mai trebuie comparat¸i cei mai put¸in semnificativi pentru c˘a nu vor schimba rezultatul

final. La compararea celui mai semnificativ bit, intr˘arile de transport se conecteaz˘a astfel ˆıncˆat s˘a semnifice

egalitatea bit¸ilor superiori (G

i

E

i

L

i

= 010). Circuitul pentru compararea a dou˘a numere de cˆate 4 bit¸i este

prezentat ˆın figura 3.21.

Figura 3.21 Circuitul comparator a dou˘a cuvinte de cˆate 4 bit¸i.

3. Cum se define¸ste not¸iunea de ”margine de zgomot”?

Solut¸ie

Marginea de zgomot (Engl. ”Noise Margin”) reprezint˘a nivelul maxim al zgomotului (tensiune electric˘a) care

poate afecta o linie de transmisiune digital˘a astfel ˆıncˆat valoarea logic˘a detectat˘a de receptor s˘a fie identic˘a cu

valoarea logic˘a emis˘a de surs˘a. Figura 3.22 prezint˘a grafic valorile de tensiune de ie¸sire generate de o poart˘a

emit¸˘atoare ¸si tensiuni de intrare la poarta receptoare. Se definesc not¸iunile:

Margine de zgomot ˆın starea H (High = 1 logic): NM

H

= V

OH

− V

IH

Margine de zgomot ˆın starea L (Low = 0 logic): NM

L

= V

IL

− V

OL

Margine de zgomot : NM = min(NM

H

, N M

L

)

Se remarc˘a atributele asociate valorilor limit˘a ale tensiunilor de intrare ¸si ie¸sire:

V

OH

- tensiune minim˘a garantat˘a la ie¸sirea port¸ii emit¸˘atoare

V

OL

- tensiune maxim˘a garantat˘a la ie¸sirea port¸ii emit¸˘atoare

3.4. Pentru cei ce vor s˘a devin˘a profesioni¸sti 47

V

IH

- tensiune minim˘a acceptat˘a la intrarea port¸ii receptoare

V

IL

- tensiune maxim˘a acceptat˘a la intrarea port¸ii receptoare

Figura 3.22 Definirea nivelelor de tensiune ¸si a marginii de zgomot pentru port¸ile logice.

4. Propunet¸i un set de valori pentru intr˘arile circuitului prezentat ˆın figura 3.23 astfel ˆıncˆat ie¸sirea s˘a fie egal˘a cu

1.

Figura 3.23 Circuitul pentru problema 4.

Solut¸ie

Pentru ca ie¸sirea F s˘a fie egal˘a cu 1 trebuie ca toate intr˘arile ˆın poart˘a AND s˘a fie egale cu 1. Pentru ca toate

intr˘arile port¸ii AN D s˘a fie 1, trebuie ca la toate intr˘arile port¸ilor N OR s˘a fie semnale cu valoare logic˘a 0.

Rezult˘a: A = 1, B = 0 ¸si C = 1.

Analitic, expresia funct¸iei este:

F = A + C · A + B · B + C

Din condit¸ia F = 1 rezult˘a:

A + C = 1 ¸si

A + B = 1 ¸si

B + C = 1.

48 LECT¸ IA 3. Port¸i logice

A + C = 1 ⇒ A + C = 0 ⇒ A = 0 ¸si C = 0, adic˘a A = 1 ¸si C = 1.

A + B = 1 ⇒ A + B = 0 ⇒ A = 0 ¸si B = 0, adic˘a A = 1 ¸si B = 0.

B + C = 1 ⇒ B + C = 0 ⇒ B = 0 ¸si C = 0, adic˘a B = 0 ¸si C = 1.

ˆ

In final, rezult˘a: A = 1, B = 0 ¸si C = 1.

5. Cum se define¸ste not¸iunea de ”fan-out”?

Solut¸ie

Not¸iunea de ”fan-out” desemneaz˘a parametrul unei port¸i logice numeric egal cu num˘arul de port¸i de acela¸si

tip ce pot fi comandate de o ie¸sire. Fiecare intrare ˆıntr-o poart˘a logic˘a conecteaz˘a o capacitate suplimentar˘a

pe ie¸sirea port¸ii care genereaz˘a semnalul. La o ˆınc˘arcare mare, ie¸sirea unei port¸i logice nu mai poate genera

un curent suficient de mare pentru a ˆınc˘arca sarcina capacitiv˘a, ceea ce va determina deteriorarea fronturilor

semnalelor digitale (fronturi mai put¸in abrupte) ¸si ment¸inerea port¸ii logice de destinat¸ie cu un semnal de intrare

ˆın domeniul interzis (ˆıntre cele dou˘a nivele de tensiune asociate st˘arilor logice 0 ¸si 1). Cantitativ, fan-out-ul unei

port¸i se define¸ste ca raportul ˆıntre curentul de ie¸sire ¸si curentul de intrare al unei port¸i logice.

Fan-out ˆın starea H (High = 1 logic): F O

H

= I

OH

− I

IH

Fan-out ˆın starea L (Low = 0 logic): F O

L

= I

OL

− I

IL

Fan-out: F O = min(F O

H

, F O

L

)